World Wide Journal of Multidisciplinary Research and Development(July 2021)

WWJMRD 2021; 7(7): 43-47 www.wwjmrd.com International Journal Peer Reviewed Journal Refereed Journal Impact Factor SJIF 2017: 5.182 2018: 5.51, (ISI) 2020-2021: 1.361 E-ISSN: 2454-6615 DOI: 10.17605/0SF.IO/RV5ZW

#### Mohamed Ibrahim. J

M.E, Maha Barathi Engineering College, Chennai, India. mimohamed5@gmail.com

**Dr. K. Somu** Maha Barathi Engineering College, Chennai, India.

Correspondence: Mohamed Ibrahim. J M.E., Maha Barathi Engineering College, Chennai, India. mimohamed5@gmail.com

# VLSI Implementation of Ternary Gates MultiValue System

# Mohamed Ibrahim. J, Dr. K. Somu

#### Abstract

CMOS logic is taken into account for implementation of solely binary logic, because the circuit complexness is increasing, the interconnection in binary occupies massive space on VLSI chip & amp; so, degrading the performance. MVL (Multi valued logic) is taken into account as resolution to the current issue. A Ternary logic or three-valued logic is taken into account as best base of many MVL systems.

The planned GATES area unit styled & simulated with the assistance of Tanner EDA tool and layout design victimization VLSI CMOS technology. Planned system: In style of digital systems, the electrical converter, NOR gate & NAND gates area unit thought-about to be building blocks. The most objective is to reduce the facility consumption & propagation delay time thereby reducing the quantity of electronic transistor.

In the planned styles, the smaller single provide voltage & amp; MOSFETs with smaller threshold voltage area unit used. 3 logic levels area unit drawn by states zero, 1, a pair of with potential (0v), (0.5v), & amp; +Vcc (+1v) severally. Within the planned styles, these output transmission gates/pull up transistors area unit eliminated from inverters, thereby reducing the part count.

Use of single power provide to implement ternary logic gates has result in important reduction in overall power dissipation & amp; rising the transition time Considering the varied benefits of the MVL, the acceptable style of MVL logic gates is vital so it'll result in the more development and its application in this area.

Keywords: VLSI, Multi Valued Logic, Ternary, Logic Gates

#### Introduction

MultipleValued logic has been the object of much research over the last 30 years. Since 1971 there has been an annual symposium devoted exclusively to the object [1]. In addition, a large number of technical papers have appeared elsewhere together with number of survey articles. Much of the older work was purely theoretical nature concerned with the functional completeness of sets of operator, functional minimization and similar problems from the switching theory and logic design. Work on hardware implementation of multiple value devices has been more recent. The application of Multi Valued Logic spans the full range of areas from application to VLSI technology and design techniques [2][3][4][5].

Recent technical work has shown some advantages of using multi-valued logic where the natural question is whether there exists a practical radix other than 2 that would produce circuits with greater saving in components, without loss of speed. Alexander (1964) showed that the most efficient radix for

implementation of switching systems is the natural base (e=2.71828). From which it appears that the closest natural integral radix should be 3 rather than 2 [6].

Ternary gives meaning of a transmission and 3- valued switching. Three-valued or ternary, logic offers several important advantages over binary logic in design of digital systems. For example, more information can be transmitted over a given set of lines or stored for a given length, the complexity of interconnections can be reduced, reduction in chip area can be achieved, and more easy error detection and error correction codes can be employed. Furthermore, serial and some serial-parallel arithmetic operations can be carried out at higher speeds. Many of these advantages have direct bearing on the implementation of digital

systems, and as a result, realizations of basic ternary gates have been proposed. These have been shown to be suitable for the design of "ternary processors" and for various other applications [7] [8] [9].

It has been reported that realization of combinational and sequential logic functions is possible in a ternary logic they element. In addition, have proposed an implementation of the T-gate using bi-polar transistors, and considered for application to the synthesis of combinational as well as logical circuits. Recently, researchers have proposed an alternative implementation of the T-gate MOS technology. The synthesis of suitable combinational circuit requires  $(3^{N}-1)/2$  T-gates where N= number of inputs. Ternary logic family comprises of set of inverters, NOR gate and NAND gate. These circuits are used to design ternary memory elements and some basic ternary arithmetic circuits like half adder and full adders, and one-ternary multiplier. The circuits thus obtained are then used to synthesize a shift register, an N-bit adder, and an N-bit multiplier.

An objective of present research work is to design and simulation of CMOS ternary logic gates (T-Gates) to implement basic ternary operations like AND, OR, NAND, NOR, NOT etc.

## **Ternary Logic Preliminaries**

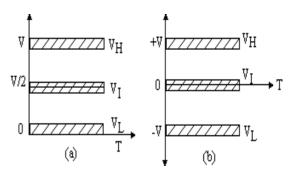

Among the MVLs, ternary logic is distinctive because of its simpler circuit realization and a well-established theoretical basis [11]. Many ternary logic models exist in the literature, but they generally involve high power consumption even in static state [12]. Customized technological processes [4] or devices [13], Current-mode MVL multi-threshold techniques also exist [10], but they are not feasible for present high performance applications as high-speed performance and low- power dissipation can be obtained using the CMOS technology. In voltage mode operation of circuit the three distinct logic levels are defined in terms of voltage where as in current mode operation, states are integral multiple of reference current. Figure 1 shows ternary levels in terms of voltage as low (V<sub>L</sub>), intermediate  $(V_I)$  & high  $(V_H)$ . Low voltage level corresponds to logical state 0; intermediate to logic state 1 & high to logic state 2 respectively. The logical symbolism assumed is given in table 1. To implement ternary system basic Boolean operations that are necessary are, ternary inverter, (T-OR/T/NOR), Ternary OR/NOR Ternary AND/NAND (T-AND/T-NAND) and Ternary EX-OR/NOR (T-EX-OR/T-EX-NOR). These operations are carried out by ternary logic gates (T-gates). Recent articles show that there is still an ongoing improvement in the implementation of T-gates [14] [15]. However, basic Tgate circuit implementations are considered in the present work using latest switching circuit devices. Haider et al. [16] introduced a new set of ternary neural networks to realize a novel TALU and used MATLAB Simulink as a simulation tool to demonstrate the feasibility, functionality and the correctness of the neural network design. Dhande et al. [17] designed and implemented 2 bit ternary ALU slice using CMOS ternary logic gates. However, in most of the studies, there still remains out-sized scope to evaluate the reductions techniques in digital designing, especially for the ternary circuits.

Fig 1: logic levels in Ternary system (a) when supply voltage is o to +v volt

(b) When supply voltage is -v to +v volt

**Table I:** Logical Symbol for Ternary System.

(a) Supply voltage 0 to +V (b) Supply voltage -V to +V

| Voltage<br>Level | Logic<br>Level |     | Voltage<br>Level | Logic<br>Level |

|------------------|----------------|-----|------------------|----------------|

| V                | 2              |     | +V               | 2              |

| V/2              | 1              |     | 0                | 1              |

| 0                | 0              |     | -V               | 0              |

| (a)              |                | (b) |                  |                |

This may further give additional circuit reduction, thereby reducing the delays and the complexity in VLSI designing. In a VLSI circuit, approximately 70 percent of the area is devoted to interconnection, 20 percent to insulation, and 10 percent to devices [18]. Ternary (three valued) or trivalent logic is an example of multi-valued logic in which the states are 0, 1 and 2

[19] which serves as a potential and a promising solution in advancements of technology

#### **A. Ternary Inverter**

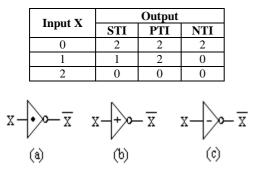

The Yoeli-Rosinfeld algebra [11] defines three basic ternary elements, the STI (simple ternary inverter) PTI (positive ternary inverter) & NTI (Negative ternary inverter) such that,

$$STI = X = 2 - X$$

$$\longrightarrow 9 \ i \to X \sigma i \qquad \dots (2.1)$$

$$PTI \quad , NTI = X^{i} = \|$$

$$\square 2 - i \to X = i$$

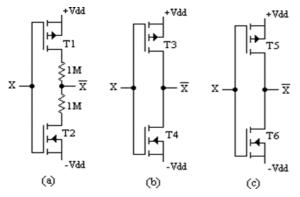

Where 'i' take the value of '2' for PTI & '0' for NTI inverter. Basic switching elements in the implementation of those inverters are transistors, MOSFET & RTDs. Because of low power consumption, less propagation time, high low power consumption, less propagation time, high fan in\out, high voltage swing and operation in GHz domain, circuits based on MOSFET of RTDs are more popular,[14][15]. Figure 2 shows MOS based three inverters namely STI, PTI & NTI. Truth table for the same is given in Table 2. Symbol for the ternary inverter is shown in figure 3.

Fig 2: CMOS implementation of T-Inverter (a) STI (b) PTI (c) (NTI).

Table II: Truth Table for Inverter.

Fig 3: Symbols for Inverters (a) STI (b) PTI (c) NTI

## B. Ternary OR /NOR circuit

Ternary OR is a circuit that have  $X_1\hbox{---} X_n$  as input &  $Y_o$  as output such that

$$T - OR = X + X + \dots + X = Max \begin{bmatrix} X \\ 1, X \end{bmatrix} \dots (2.2)$$

Ternary NOR has an output that is a compliment of OR function i.e.

$$T - NOR = X + X + \Box + X = -\frac{1}{Max [X, X_{2} \dots X_{n}]} \dots (2.3)$$

The sign + indicates logical ternary OR operation. Inverter is a basic circuit that is used for implementing T-OR/NOR functions [11]. Depending upon the type of inverter used, the logic functions T-OR/NOR can be a) simple ternary OR/NOR [ST-OR/NOR], b) Positive ternary OR/NOR [PT-OR/NOR], c) Negative ternary OR/NOR [NT-OR/NOR]. Fig 4 shows Symbols for T-OR/NOR logic gates.

Fig 4: Symbols for T-OR/NOR logic gates (a) ST-OR (b) PT-OR (c) NT- OR (d) ST-NOR (e) PT-NOR (f) NT-NOR.

## III. Design and Simulation of the Ternary Gates.

Tanner Tool is reported to be potential EDA software for designing and verification of various VLSI circuits. The T-gates designed in this paper are implemented using Tanner tool, version 13.02 on machine of core 2 duo processor, 2 GHz,

1 GB RAM. S-Edit, L-Edit, T-Spice and W-Edit are the

prominent subsets of the tanner tool that are used to derive the various device parameters and further verify the functionality of the gates. The gates in the original binary logic diagram of the circuit are conceptually transformed into corresponding ternary ones using the injected voltage method [20].

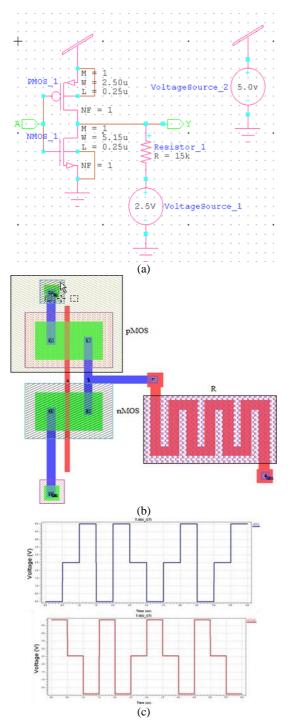

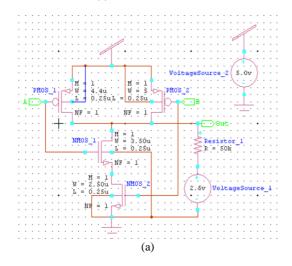

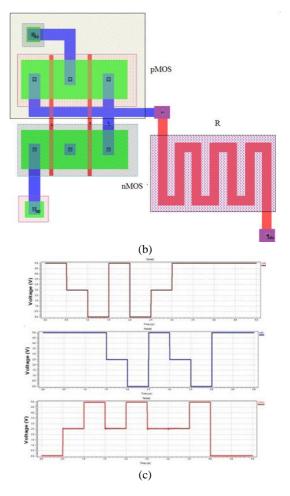

This paper uses three voltage levels (0 V, 2.5 V, 5V) to represent three ternary logic levels (0, 1, and 2). Figure 6(a)depicts a simple ternary inverter (STI) which is composed of nMOS, pMOS and a resistor 'R'. Vdd (voltage source 1) is 5V and auxiliary power supply (voltage source 2) is 2.5 V. The absolute value of thresholds (VTp, VTn) is raised for the MOS transistors, wherein VTp = -3.75Vand VTn = 3.75 V. This is accomplished by changing W/L (Width / Length) ratio of the MOS transistors and the corresponding multiplier factor 'M'. When input level is 2.5 V, both pMOS and nMOS transistors and the output nodes will be 2.5V due to the connected auxiliary supply. Obviously, on the resistor there will be a current of 2.5 V/R drawing out of the auxiliary supply if the node value is 0 V, and a current of 2.5 V/R injecting into the auxiliary supply if the node value is 5 V. The layout is designed using L-edit as depicted in figure 6(b). Both, the layout and the schematic of the STI are independently verified using T-spice and W edit. Figure 6 (c) illustrates the simulation results of STI, verified for all the combinations of the input. Other universal gates, T-NAND and T-NOR have also been implemented in a similar fashion. Figure 7 indicates the schematic, layout and simulation results of the T-NAND. Encouraging results are obtained for T-NOR gate as well.

Additional performance analysis of the designed basic gates has been carried out in terms of calculating the rise time and fall time during all the logic transitions (0-1, 1-2 and 0-2). The average dissipated power across the resistor and the MOS transistors is also obtained. Table 3 and Table 4 summarizes the achieved results.

Table III: Timing Parameters of the Ternary Gates.

| Parameter | Logic level | TNOT    | TNAND   | TNOR    |

|-----------|-------------|---------|---------|---------|

| Rise Time | 0 to 1      | 0.74 ns | 2.32 ns | 2.02 ns |

| Rise Time | 1 to 2      | 0.74 ns | 1.47 ns | 1.38 ns |

| Rise Time | 0 to 2      | 1.69 ns | 0.50 us | 0.50 us |

| Fall Time | 2 to 0      | 0.50 us | 2.50 us | 1.62 ns |

| Fall Time | 2 to 1      | 1.58 ns | 2.10 ns | 0.71 ns |

| Fall Time | 1 to 0      | 1.43 ns | 0.73 ns | 0.71 ns |

Table IV: Performance Parameters of the Ternary Gates

| Average Power   | TNOT     | TNAND    | TNOR     |

|-----------------|----------|----------|----------|

| MOS Transistors | 0.289 uw | 1.216 uw | 75.62 uw |

| Resistor        | 0.378 mw | 3.103 uw | 98.77 uw |

Fig 6: Results of TNOT gate (STI gate) (a) schematic (b) layout (c) simulation results.

Fig 7: Results of TNAND gate (a) schematic (b) layout (c) Simulation results.

## Conclusion

Tanner tool has been exploited to design and implement CMOS Ternary logic gates. The layouts and the simulation results along with performance analysis is also been presented in the paper. The Voltage values for the ternary logic levels were tested for STI, ST-NAND and ST-NOR. The same procedure can be easily extended to design positive and negative ternary logic gates by adjusting the auxiliary supply voltage at 0V and -2.5 V respectively.

The choice of the resistance value greatly affects the voltage levels at the output of the T-gates. This paper examines the performance of designed T gates to estimate the suitable value of resistance. Encouraging results are obtained with R= 15 K in case of STI whereas ST-NAND and ST-NOR give best results with R=50 K. The value of R thus varies with the design. W/L ratio is another important parameter that has a significant impact on the design of the T-gates. This ratio affects the threshold voltage of the MOS transistors. In the proposed design, W/L ratio is suitably maintained to achieve desired voltage values at the output.

## References

- 1. 'Introduction-Multiple-valued logic' special issue IEEE transaction on computer Vol. C-35, No.2, Feb1986.

- Muzio J.C. & Wesselkamper T.C. 'Multiple Valued Switching Theory' Bristol & Boston: Adam Hitger Ltd. 1986.

- 3. Porat D.I. 'Three valued digital Systems' Proc. IEE, Vol. 116. No.6, PP. 947-954, June 1969.

- Balla P.C. & Antoniou A. 'Low Power dissipation MOS ternary Logic Family' Proc. IEEE Journal of solid state circuits, vol. SC- 19 No.5, pp.739-749, October 1984.

- S.P. Onneweer and H.G. Kerkhoff, "High-radix current-mode CMOS circuits based on the truncated difference operator," Proc. IEEE ISMVL, pp. 188-195, May 1987.

- 6. M. A. H. Abdul–Karim 'A ternary J-K memory' Proc. IEE ISMVL pp.221-225.May 1976.

- Huber J.L., Chen J, McCormack, Zhuow. of Reed M.A. 'An RTD/Transistor switching block & its possible application in binary & ternary adders' Proc. IEEE Trans. on Electron Devices, Vol. 44 No.12, pp.2149-2152,December 1997.

- 8. Swamy M.N.S. 'A high speed tunnel diode scaler' Electron Engg. Vol.37, pp 225-229, 1965.

- 9. Wang s., Wu xunwei & Feng H. 'The high-speed ternary logic gates based on multiple B transistors. Proc ISMVL, pp.178-181, May 1995.

- 10. Current K.W. 'Current mode CMOS Multiple-valued logic 1994 Circuits' IEEE Journal of Solid-State circuits, Vol-29, No.2, PP.95-906, Feb 1994.

- M. Yoeli, G. Rosenfeld, "Logical Design of ternary switching circuits," IEEE Trans. Computer, Vol. C-14, pp. 19-29, Feb. 1965.

- 12. J.S. Wang, C.Y. Wu, M.K. T Sai, "Low Power dynamic ternary logic", Proc. IEE, vol. 135, pt. G. pp. 221-230, Dec. 1988.

- 13. X Wu, F. Prosser, "CMOS ternary logic circuits", Proc. IEE-G, Vol. 137, No.1, pp. 21-27, Feb. 1990.

- 14. Resonant Funneling Device Logic Circuit technical report July 1999.

- P.Fay, H.H. Bernstein, D.Chow 'Integration of InAs / AlSb/ GaSb Resonant inter band tunneling diodes with HFET for ultra-high-speed digital applications. Proc. IEEE special issue on Electron Devices, 1999.

- Ali, H., Hamdam, M., Rashid, M., Hamied, H., Issa, A., Kassem, A.: 'A novel neural network ternary arithmetic logic unit', The 23<sup>rd</sup> international technical conference on circuits / systems, computers and communications (ITC-CSCC 2008), pp. 593-596.

- 17. Dhande, A., Ingole, V.: 'Design and implementation of 2 bit ternary ALU slice' 3<sup>rd</sup> International conferences sciences of electronics, technologies of information and telecommunication, march 2005, Tunsia pp. 1-11

- Gorde, K., Deshmukh. P.: 'Design and Simulation of Ternary Logic Based Arithmetic Circuits', Proceedings of the 2009 International Conference on Signals, Systems and Automation (ICSSA 2009). Universal-Publishers. Com, 2010.

- Kotiyal, S., Himanshu, T., Nagarajan, R.: 'Design of A ternary barrel shifter using multiple valued reversible logic', Proceeding of 10<sup>th</sup> IEEE international conference on nanotechnology joint symposium with nano korea 2010, pp. 1104-1108.

- 20. H. T. Mouftah, K. C. Smith, 'Injected voltage low power CMOS for 3 valued logic' IEE Proceeding, vol 129, Pt G, No. 6, Dec 1982.